(3 Hours)

[ Total Marks: 100

5

5

5

8

12

N.B. :

- (1) Question No.1 is compulsory.

- (2) Attempt any four questions from rest.

- (3) Make any suitable assumption wherever required.

- (4) Use of semilog paper or graph paper is necessary wherever applicable.

- 1. (i) Explain why is the phase Margin increased above that desired when designing a lag compensator.

- (ii) Briefly describe the configuration of an observer.

- (iii) Explain the region of stability on the z-plane

- (iv) Explain the advantage of I-P controller over PI controller.

- 2. (a) Design the value of gain k for a gain margin of 12 dB in the unity feedback system if the open loop transfer function is

$$G(s) = \frac{k(s+2)}{s(s+3)(s+4)(s+6)}$$

(b) Given a unity feedback system with

$$G(s) = \frac{k(s+10)(s+11)}{s(s+3)(s+6)(s+9)}$$

Use frequency response method to design a lag compersator to yield Kv =1000 and 15% overshoot for the step response. Make any required second order approximation.

3. (a) Design a state variable reedback controller to yield a 20.8% overshoot 15 and a settling time of 4 second for a plant.

$$G(s) = \frac{s+4}{(s+1)(s+2)(s+5)}$$

that is represented in cascade form.

(b) Compare the major difference in the transient response of an observer to that a controller. Why does this difference exist.

TURN OVER

RJ-Con. 11838-15.

10

10

4. (a) Consider the plant

$$\dot{\mathbf{x}} = \begin{bmatrix} 0 & 1 \\ -3 & -5 \end{bmatrix} \mathbf{x} + \begin{bmatrix} 0 \\ 1 \end{bmatrix} \mathbf{u}$$

$$\mathbf{y} = \begin{bmatrix} 1 & 0 \end{bmatrix} \mathbf{x}$$

Design a controller without integral control to yield a 10% overshoot and a settling time of 0.5 sec. Repeat the design with integral control.

(b) Using partial fraction expansion, find the z-transform for

G(s) if T = 0.5 sec G(s) =

$$\frac{s+4}{(s+2)(s+5)}$$

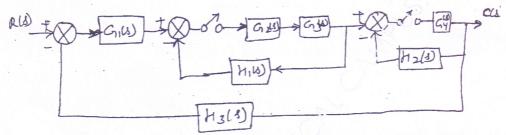

5. (a) Find G (z) = C (z) / R (z) for the given block diagram if T = 0.3 sec 10

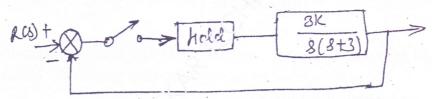

(b) Find the range of gain K to make the system shown in fig. below stable. 10

- 6. (a) Explain the logic behind the selection of PID controller in control system 10 design.

- (b) Explain the scan cycle of execution in PLC. 5

- (c) Explain the use of start, stop and interlock circuit in PLC programming 5 with the help of suitable small example.

- 7. (a) Properly explain in detail the Timer ON instruction and Move instruction 10 of PLC with the help of two distinct example.

- (b) Explain the importance and use of data file of PLC.

- (c) Explain different type of addressing modes used in PLC. 2